21 Aug A ‘Track and hold’ External VFO for tuning older (‘boat anchor’) radios

by Jim Sosnin VK3JST

CAUTION

Radios such as the Yaesu FT-101Z featured in this article, from the valve era, are potentially lethal if the case is opened up to access internal wiring, as they contain high voltage power supplies. Please do not attempt this project unless you have experience working with this type of equipment. Switching mains power off and unplugging the power lead is not sufficient to ensure safety. The large HT electrolytic capacitors can hold their charge for a long time after mains power is removed, and even longer if the original bleed resistor has failed, or an external bleed resistor has not been applied correctly.

Introduction

Many older radios, built forty or more years ago, remain in regular use by radio amateurs. Unlike their modern counterparts, which feature various forms of digital frequency generation/control, the transceivers from that era are tuned via a VFO whose design is entirely analog. They can still perform remarkably well, apart from an initial frequency drift during warmup. Nevertheless, they fall short of the stability and precision we expect today. Some operators circumvent this by tuning the radio with an external, digital VFO, the frequency being adjusted via a rotary encoder or entered directly via a touchscreen or numeric keypad.

That approach has a downside, however. It renders the radio’s existing tuning mechanism redundant; the user loses the satisfaction of operating an ‘intact’ radio, with its silky smooth gear drive on the tuning shaft. Hence this Arduino-based project, whereby the radio’s ‘Internal VFO’ mode is selected whenever the frequency needs to be changed, allowing the existing mechanism to be used. Then, when the frequency needs to stay constant, ‘External VFO’ is selected; this also switches a digital ‘slave’ VFO, which has been tracking the internal VFO’s frequency, into ‘hold’ mode, to keep the radio exactly on frequency. This allows the operator to focus on the QSO without the distraction of having to check that the radio remains tuned correctly, especially if using the radio soon after switch-on, while it is still warming up.

The design includes a self-calibration feature, requiring the user only to change an on-board jumper link temporarily and press two buttons. Any tracking error, present before calibration, is measured by the software, which then calculates and stores a correction factor in on-chip EEPROM. The correction factor is subsequently read from EEPROM at each Arduino startup. The self-calibration procedure could be done just once, and then left as-is, but it is such a quick and easy process that some users may choose to recalibrate every few months or so, especially if tracking errors creep in over time. This may happen with ageing of components such as the crystals for clocking the Arduino and the digital VFO modules.

A companion project – a digital frequency display – is described here as well, because for my prototype construction, I’ve housed both projects in the same enclosure. However, the digital frequency display is not required if the radio already has one, as many do.

My radio is a Yaesu FT-101Z (without a further ‘D’ suffix). It was built in 1981, towards the end of the FT-101 series, which had been in production since 1970. It’s worth noting that a digital frequency display had become available by this time, either as standard in the FT-101ZD model, or as a user-installable upgrade. However, even in the FT-101ZD, and similar radios from other manufacturers, the actual tuning process was still reliant on an analog VFO. Fortunately, a common feature of these radios is the presence of an ‘External VFO input’ connector on the back panel, and an ‘Internal/External’ VFO selection switch.

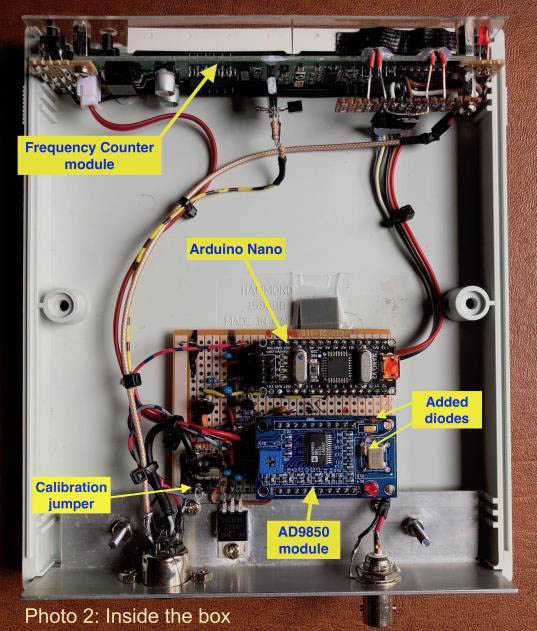

I bought a Sanjian frequency counter module to use as my digital frequency display, and built my prototype Track/hold VFO using two further modules: an Arduino ‘Nano’ (for control) and an AD9850 DDS (Direct Digital Synthesiser, to generate the slave VFO signal), both mounted on VeroBoard along with some other components. This fitted easily into a plastic box which also houses the frequency counter module. Photo 1 shows the box sitting on top of the radio.

The photo above shows an inside view of the box. The frequency counter module occupies only a 30mm depth at the front of the box, leaving plenty of space inside for the Track/hold VFO.

Downloads

Design Considerations

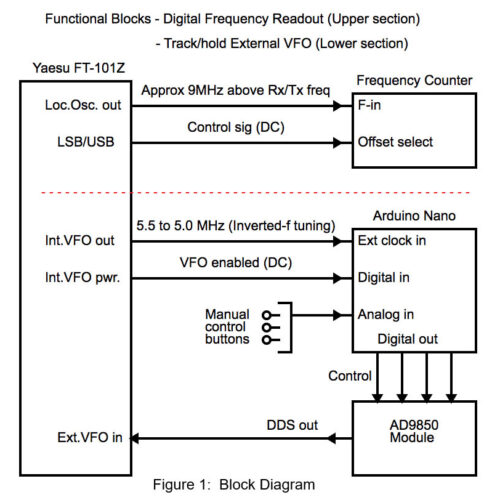

Figure 1 shows the Digital Frequency Display and the Track/hold VFO as separate functional blocks (above and below the dotted line). Within the radio, the circuits they connect with are (using Yaesu’s terminology) the ‘pre-mix’ type LO (Local Oscillator) and the VFO. Since the radio’s tuning depends on both of these, they warrant a brief overview.

The VFO output is always in the range 5.0 to 5.5MHz, to provide tuning over a 500kHz HF band segment. The LO is generated via a combination of the VFO output and another, higher frequency signal, derived from one of a bank of crystal oscillators (one per band).

The VFO actually tunes ‘inversely’, as it is the difference frequency that is used from the pre-mix LO output. For example, if the radio is being tuned across the 80m band from 3.5MHz to 4MHz, the VFO frequency will be decreasing from 5.5MHz down to 5.0MHz.

The end product is the LO output. Its frequency is always at a constant offset above the radio’s Rx/Tx frequency. In the FT-101Z, this offset (ie the radio’s IF) is approx 9 MHz.

A further complication here for the frequency counter module is that there are actually two offsets that need to be configured for it, for ‘correct’ representation of the Rx/Tx frequency. The offsets for LSB and USB modes must differ by 3kHz. This is because, by convention, we expect the digital readout to display the (suppressed) carrier frequency, rather than the centre of the Rx/Tx passband. If the frequency display is for an FT-101Z, the exact offsets are -8.989MHz (LSB) and -8.986MHz (USB). They will be different for other radios. Note that both offsets are negative values.

I chose the Sanjian PLJ-8LED-C frequency counter module for my frequency display because it provides two user-configurable frequency offsets; these are stored in the counter’s EEPROM, and are selectable at run time via a control voltage on one of the module’s connector pins. It also features a TCXO for improved stability. Other suitable frequency counter modules are probably available. If the module is to be housed inside the radio, instead of in an external box like my prototype, it must a smaller type in order to fit behind the clear section in the radio’s front panel. And of course, some amateurs might prefer to build their own from a kit or from scratch. The counter’s input frequency range needs to extend reliably to at least 39MHz (the radio’s maximum LO frequency for Rx/Tx in the 10m band).

The remaining functional blocks in figure 1, below the dotted line, constitute the main focus of this project: the track/hold VFO itself. An Arduino ‘Nano’ module is the controller and an AD9850 DDS module is the digital (slave) VFO. The Arduino program, in typical fashion, runs as a repeating loop; in this project it cycles every 100mSec (approx). Each time around the loop, it performs three main tasks:

(1) It counts cycles from the radio’s internal VFO output, ie measures its frequency. The resolution is 10Hz (the inverse of the 100mSec gate time). Since the highest frequency generated by the VFO is well under 6MHz, it is within the capabilities of the ATmega328P processor in the Arduino. Yes, we already have a frequency counter displaying the radio’s Rx/Tx tuning, but this additional one exists only in software and has no display.

(2) It monitors the internal VFO’s DC supply, which sits at +6V when the radio is in ‘Internal VFO’ mode, but drops to 0V when the user switches to ‘External VFO’, via front panel buttons on the radio. The program thus knows whether to continue running in ‘Track’ mode, or to switch to ‘Hold’ mode.

(3) In Track mode, the Arduino updates the DDS with its latest frequency count, appropriately scaled, to keep it tracking the analog VFO’s frequency; both VFOs thus respond identically to any tuning changes made by the user, apart from the 100mSec lag in the DDS update. During Track mode the DDS output is not used in the radio. However, in Hold mode, the Arduino stops updating the DDS, allowing its frequency to remain set on the most recent count obtained when it was in Track mode. During Hold mode, the radio obtains its VFO signal from the DDS via its ‘External VFO’ input.

The Arduino also monitors the state of three Manual Control Buttons, and controls three status LEDs. Two of the buttons are frequency ‘Nudge’ up/down buttons. They are disabled during Track mode, but in Hold mode they allow the DDS frequency to be adjusted up or down slightly if required, without the need to switch back and forth between internal/external VFO modes on the radio merely to use the tuning knob briefly. The Nudge buttons change the frequency by just 5Hz when pressed momentarily. Larger changes are accomplished by holding the button down, generating a repeat sequence of 5Hz steps up or down, at the rate of 10 steps/sec.

The third button is a ‘Lock’ button, which allows the DDS frequency update to be disabled, even when the radio has been switched back to ‘Internal’ VFO. Think of it as a ‘VFO A/B’ feature. The button toggles the system between Locked and Unlocked states on alternate presses. Unlike the Nudge buttons, this one does not generate repeat actions if it is held down. When the system is in Locked mode, the radio’s ‘Int/Ext’ VFO buttons allow the user to swap between tuning around the band, or recalling the previously stored frequency. One of the LEDs indicates Locked/Unlocked status.

The other two LEDs indicate whether the system is in Track or Hold mode. In effect, they follow the user’s selection of Internal or External VFO on the radio, but, as photo 1 shows, I chose to label them ‘Tune (VFO)’ and ‘Hold (DDS)’ to reflect the current user operation. However, these LEDs are not essential, because the radio has its own ‘Int/Ext’ VFO status LEDs. The two additional LEDs could be omitted, especially if the radio already has, or is about to have, an internally housed digital frequency display. It would then make sense for the whole project, including the Track/hold VFO, to be housed inside the radio instead of in an external box.

Further details of the software design and operation can be found in the numerous comments I’ve included in the Arduino source code file for this project, ‘Tracking-VFO-VK3JST.ino’. To download it, click the icon located down at the end of this article. It is best viewed within the Arduino development environment, for correct text colours distinguishing comments and other text types, such as code keywords, from each other. However, it is just a text file, so if you change the ‘.ino’ extension to ‘.txt’, you can view it in any word processor or text file viewer.

Circuit Description

At the top of the schematic diagram (Figure 2) is the optional frequency display. As already noted, this is not needed if the radio already has one. It is powered from the +8V DC rail in the radio, but has an internal regulator, reducing it to 5V. The radio’s VFO output connects directly to the counter via shielded coax. The radio’s LSB/USB status (0V or +8V level) connects via Q1, an inverter stage whose main purpose is to reduce the logic level down to the 5V needed by the counter at its ‘Offset select’ control input header. That header also provides +5V to R3, the pullup for Q1.

All the remaining components, for the Track/hold VFO itself, operate from a separate +5V supply derived from the radio’s +8V rail via regulator U1.

The radio’s VFO output is buffered by Q2, a unity gain buffer stage which reduces loading on the VFO output. The connection is actually via a jumper link, allowing Q2 to receive its input either from the radio’s VFO (normal setting, via top and middle pins linked)), or from the DDS output (calibration setting, with middle and bottom pins linked). Q3 amplifies the 300mV P-P VFO sinewave signal to around 4V P-P to feed the external clock input for one of the counter/timers in the Arduino, via pin D5 (Digital i/o pin 5). This 4V P-P waveform is no longer a sinewave, as it is swinging well beyond the linear range of Q3, but this makes it more suitable for the Arduino clock input.

TP1 is a test point for an oscilloscope check of the waveform. In my prototype, its amplitude was 4V P-P, swinging from +0.5V to +4.5V. I found that it needs to be at least 3.5V P-P, otherwise the Arduino will not be able to count the waveform pulses reliably. Expect it to look less like a sine wave, and more like a square wave with rounded corners. The duty cycle should be close to 50%; some experimentation with component values for R7, R8 and possibly C7 may be necessary to achieve all this, depending on the characteristics of Q3. The hFE of the ones in my batch measured around 230.

The radio supplies +6V DC to power its VFO when switched to ‘Int’ VFO. This 0V/+6V line is conditioned by Q4 and sensed at the Arduino D2 digital input, to tell the Arduino whether the user has selected Int or Ext VFO on the radio. Q4, like Q1, switches a 0V/+5V logic range at its collector, but Q4’s collector load is an Arduino internal pullup, enabled inside the ATmega328P chip via software.

Arduino digital i/o pins D3, D4, D6 and D7 are configured as outputs. They control the DDS module via its serial data transfer mode, which requires fewer connections than the parallel mode. The serial mode selection is ‘hard-wired’ using DDS module pins D0 and D1 (connected to +5V via R19), and D2 (grounded). The remaining DDS ‘parallel transfer’ pins D3 to D7 are not connected. It may actually be possible to also omit the connection between Arduino D3 and DDS Reset, and simply ground the DDS Reset pin, as the Reset appears to be required only for some configurations and processes which are not used in this project. However, the datasheet is not clear on this point, so I felt it would be safer to retain the software Reset capability.

The DDS IC provides a pair of complementary outputs, Zout1 and Zout2, although only Zout2 passes through a smoothing filter to remove digital synthesis artifacts from the signal on the way to the Zout2 pin on the module. I’ve chosen to use Zout1 only during calibration. It connects via attenuator R18/R17 to the normal/cal jumper header.

Zout2 feeds the Ext. VFO input on the radio, via an attenuator comprising R21 and bias resistors R20 and R23, then via buffer/gate Q5. In parallel with R23 is Q6, which reduces the forward bias on Q5 when the user has selected Internal VFO (ie when the slave VFO is in Track mode, and ‘catching up’ to the tuned frequency every 100mSec, and not yet generating a constant frequency). This turns Q5 off, and prevents the slave VFO’s output from escaping into the radio prematurely, as this would increase the likelihood of spurii.

The third button is a ‘Lock’ button, which allows the DDS frequency update to be disabled, even when the radio has been switched back to ‘Internal’ VFO. Think of it as a ‘VFO A/B’ feature. The button toggles the system between Locked and Unlocked states on alternate presses. Unlike the Nudge buttons, this one does not generate repeat actions if it is held down. When the system is in Locked mode, the radio’s ‘Int/Ext’ VFO buttons allow the user to swap between tuning around the band, or recalling the previously stored frequency. One of the LEDs indicates Locked/Unlocked status.

Calibration

Note that a computer connection is not required for this, as the calibration process is entirely stand-alone. However, if you wish to see some progress and status messages during the process, connect a computer to the Arduino Nano via a USB cable (but only after the radio is already switched on, otherwise many other parts of the circuit will be attempting to draw power through the Nano, from the computer’s USB port). Then run the Arduino Serial Monitor, with 9600 baud selected.

The calibration sequence is quite straightforward to step through, despite the longish description below. I expect it may take longer to read through it than to actually do it!

- Power the system up and leave the radio switched to ‘Int VFO’ until calibration is complete.

- Relocate the ‘Calibration’ jumper link to the ‘Calib’ position. This connects the DDS output to the Q2/Q3 circuitry feeding the Arduino ‘External clock’ input.

- Press and release the Arduino ‘reset’ button, while holding either of the ‘Nudge’ (up or down) buttons pressed.

- Keep the Nudge button pressed until the ‘Lock’ LED starts flashing, then release it. The Lock LED flashes for a few seconds, indicating that calibration is in progress. After the Lock LED stops flashing it should remain lit, indicating that calibration is complete; it also indicates that the system has been set to Lock mode (appropriate at this point, as normal tracking cannot be resumed until the jumper setting is restored).

- Set the jumper link back to its ‘Normal’ position. This reconnects the radio’s internal VFO output to Q2/Q3 feeding the Arduino ‘External clock’ input.

- Press and release the ‘Lock’ button to toggle the system back into Track mode. Check the tracking by switching the radio VFO selector between ‘Int’ and ‘Ext’. The Digital Frequency Display should indicate the same frequency in each case.

Additional notes

A detail which I have not shown on the schematic is a pair of diodes that I have added to lower the supply voltage to the 125MHz crystal oscillator module, which is the DDS clock generator on the DDS module. They can be seen in photo2. The datasheet for the AD9850 chip specifies that it can be powered from either 3.3V or 5V, and the DDS module manufacturers have specified that same operational range for the module as a whole. However, I was concerned that the clock generator might have a 3.3V rating only, like others in its family. I couldn’t find a datasheet that was an exact match though, so it may turn out to be 5V tolerant after all. In the meantime, I did not want to risk overdriving the crystal, and since everything still worked reliably with 5V supplying the DDS, but with a reduced DC supply to the clock generator (approx 3.6V after the 2 diodes), I’ve left it that way for now.

Some other details which are not provided here are in regard to the connections already available on the radio, and some additional ones that require tapping on to internal wiring points. Rear panel connections differ between different models in the Yaesu FT101 series, and, in fact, even between the MkI, MkII and MkIII variants of the FT101-Z model. I expect that anyone considering replicating this project would already be quite familiar with their own make/model of radio, and have access to schematics and detailed documentation.

However, as a rough indication of what might be involved, here is what I found with my FT101-Z MkIII:

The LO output was available via an RCA coax socket accessible inside the radio (intended for the optional digital frequency display). On the rear panel, a 6-pin DIN socket provided the Ext VFO input connection. Beside it, an 8-pin ‘DIN-look-alike’ socket almost provided the Int VFO output, the switched +6V DC (Internal VFO mode) and the switched +8V DC (USB mode). However, this is not a standard 8-pin DIN socket, as it includes a switch mechanism for Int/Ext VFO path.

More importantly, the pin spacing is slightly different to a standard 8-pin DIN, so I ended up adding a third DIN socket on the rear panel, in the pre-existing cutout provided originally for an optional connection to a DC-to-HT inverter power supply. I wired this additional socket to carry the Int VFO output and the switched +6V and +8V, tapped off the original 8-pin socket, and also the 0V and +8V power rails, tapped off a terminal board inside the radio. There were spare pins still available so I also brought the LO output coax out to this socket, from the internal RCA connector.

Jim Sosnin

No Comments